Open-Source Internship opportunity by OpenGenus for programmers. Apply now.

Reading time: 15 minutes

Abstraction is a very important concept in our society.

Considering any field of study, there is a baseline or a basic set of knowledge or operations. You may see this as the level of simiplicity of the basic knowledge. For example, consider basic arithmetic, there are two possible set of operations:

- Operations such as add, subtract, multiply and divide

- Operations such as bitwise and, or, xor

With both approaches, we can achieve the same thing yet the procedure will be very different. Computers uses the second set yet we prefer to use the first set. One evident difference is the in the first set, we deal with compressed form of data yet in the second set, we deal with expanded form of data.

In this view, computers need to make similar decision such as whether to support basic operations like add only or have built-in support for high level operations such as multiplication and division. This has lead to the development of two instruction set namely:

- Reduced Instruction Set Computer (RISC)

- Complex Instruction Set Computer (CISC)

We will look into Reduced Instruction Set Computer (RISC) in this article.

Computer Performance

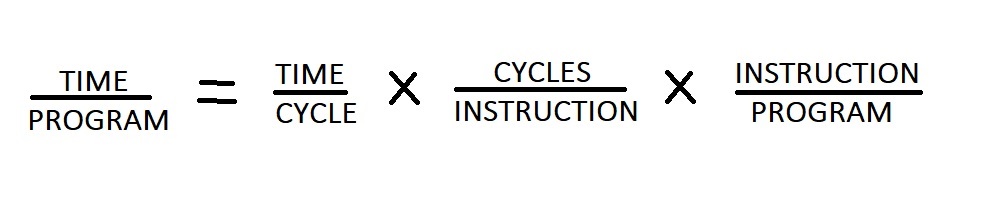

The performance of any computing device is denoted by the following equation:

Thus, the performance is inversely proportional to:

- time taken per cycle

- cycles per instruction

- number of instructions in a program

The time taken per CPU cycle is dependent to the hardware material to some extend and we will not concentrate over this.

The RISC architecture focuses on reducing the number of cycles per instruction.

The RISC Approach

RISC processors only use simple instructions that can be executed within one clock cycle.

Thus, the multiplication "MULT" command will be divided into three separate commands:

- "LOAD," which moves data from the memory bank to a register

- "PROD," which finds the product of two operands located within the registers

- "STORE," which moves data from a register to the memory banks.

In order to perform the multiplication, a programmer would need to code four lines of assembly:

LOAD A, 2:3

LOAD B, 5:2

PROD A, B

STORE 2:3, A

At first, this may seem like a much less efficient way of completing the operation. Because there are more lines of code, more RAM is needed to store the assembly level instructions. The compiler must also perform more work to convert a high-level language statement into code of this form.

However, the RISC strategy also brings some very important advantages. As each instruction requires only one clock cycle to execute, the entire program will execute in approximately the same amount of time as the multi-cycle "MULT" command.

These RISC "reduced instructions" require less transistors of hardware space than the complex instructions, leaving more room for general purpose registers. Because all of the instructions execute in a uniform amount of time (i.e. one clock), pipelining is possible.

Separating the "LOAD" and "STORE" instructions actually reduces the amount of work that the computer must perform. After a CISC-style "MULT" command is executed, the processor automatically erases the registers. If one of the operands needs to be used for another computation, the processor must re-load the data from the memory bank into a register. In RISC, the operand will remain in the register until another value is loaded in its place.

RISC Roadblocks

Despite the advantages of RISC based processing, RISC chips took over a decade to gain popularity in the commercial world. This was largely due to a lack of software support.

Although Apple's Power Macintosh line featured RISC-based chips and Windows NT was RISC compatible, Windows 3.1 and Windows 95 were designed with CISC processors in mind. Many companies were unwilling to take a chance with the emerging RISC technology.

Without commercial interest, processor developers were unable to manufacture RISC chips in large enough volumes to make their price competitive.

Another major setback was the presence of Intel. Although their CISC chips were becoming increasingly unwieldy and difficult to develop, Intel had the resources to steer development and produce powerful processors. Although RISC chips might surpass Intel's efforts in specific areas, the differences were not great enough to persuade buyers to change technologies.

The Overall RISC Advantage

Today, the Intel x86 is arguable the only chip which retains CISC architecture. This is primarily due to advancements in other areas of computer technology. The price of RAM has decreased dramatically. In 1977, 1MB of DRAM cost about $5,000. By 1994, the same amount of memory cost only $10. Compiler technology has also become more sophisticated, so that the RISC use of RAM and emphasis on software has become ideal.

Key points of RISC architecture

- Emphasis on software

- Single-clock, reduced instruction only

- Register to register: "LOAD" and "STORE" are independent instructions

- Low cycles per second

- large code sizes

- Spends more transistors on memory registers